# 描述

MX74502D23 控制器与外部背对背连接的N沟道MOSFET配合工作,可实现低损耗反极性保护和负载断开的解决方案。该器件也可以配置为具有过压保护功能的负载开关,用于驱动高侧MOSFET。3.2V至90V的宽电源输入范围可实现对众多常用直流总线电压(例如,12V、24V和48V输入系统)的控制。该器件可以承受并保护负载免受低至-90V的负电源电压的影响。

MX74502D23控制器为外部N沟道MOSFET提供电荷泵栅极驱动。当使能引脚处于低电平时,控制器关闭,消耗大约1μA的电流,从而在进入睡眠模式时提供低系统电流。MX74502D23还具有可编程的过压保护和欠压保护功能,可在发生故障时将负载从输入源切断。这些器件采用8引脚DNF2\*3-8L封装,额定工作温度范围为-40℃至+150℃

# 特性

- ◆ 3.5V至90V输入范围(3.9V启动)

- ◆ -90V反向电压额定值

- ◆ 集成电荷泵用于驱动 外部背对背N沟道MOSFET 外部高侧开关MOSFET 外部反极性保护MOSFET

- ◆ 2.3A峰值栅极灌电流能力

- ◆8mA峰值栅极驱动1拉电流能力

- ♦ 使能引脚特性

- ◆ 150μA典型工作静态电流(EN=高电平)

- ♦ 1μA关断电流@12V input (EN=低电平)

- ◆ 可调节过压和欠压保护

- ◆ -40℃至+125℃环境工作温度范围

- ◆ 采用8引脚DFN2\*3-8L封装

# 应用

- ◆ 工业工厂自动化和控制-PLC数字输出模块

- ◆ 工业电机驱动

- ◆ 工业运输

- ◆ 电源反极性保护

# 基本信息

## 订购须知

| 产品编号       | 描述        |

|------------|-----------|

| MX74502D23 | DFN2*3-8L |

| MPQ        | 3000pcs   |

#### 封装耗散额定值

| 封装        | RθJA(°C/W) |

|-----------|------------|

| DFN2*3-8L | 65         |

## 绝对最大额定值

| 参数                             | 范围                                         |

|--------------------------------|--------------------------------------------|

| VS to GND                      | -100 to 100V                               |

| EN/UVLO,OV to GND,Vvs>0V       | -0.3 to 100V                               |

| EN/UVLO,OV,Vvs≤0V              | V <sub>VS</sub> to 100+V <sub>VS</sub>     |

| SRC to GND,V <sub>VS</sub> ≤0V | V <sub>VS</sub> +0.3V(MAX)                 |

| SRC to GND,Vvs>0V              | -(100-V <sub>VS</sub> ) to V <sub>VS</sub> |

| GATE to SRC                    | 0 to 15V                                   |

| VCAP to VS                     | -0.3 to 15V                                |

| 结温,Tı                          | -40 to 150°C                               |

| T <sub>stg</sub>               | -40 to 150°C                               |

超出绝对最大额定值的应力可能会对设备造成永久性损坏,这些仅是应力额定值,不意味着设备在这些或任何其他超出"推荐条件"下指示的功能操作。长时间暴露在绝对最大额定值条件下可能会影响设备可靠性。

# 推荐操作条件

| 参数                      | 范围           |

|-------------------------|--------------|

| VS to GND               | -90 to 90V   |

| EN/UVLO, OV, SRC to GND | -90 to 90V   |

| Cvs                     | 100nF-2μF    |

| Cvcap-vs                | 1μF          |

| GATE to SRC             | 15V          |

| 结温,T <sub>J</sub>       | -40 to 150°C |

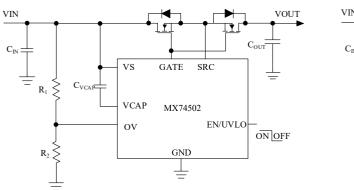

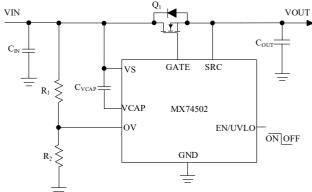

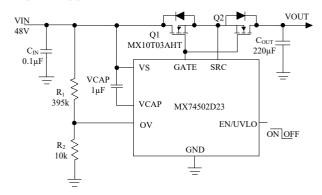

# **Typical Application**

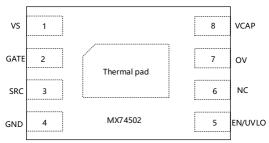

# **Terminal assignments**

MX74502D23

| Pin         |     | Description                                                                                                                                                                                                                                                                                                                                 |  |  |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name        | No. | Description                                                                                                                                                                                                                                                                                                                                 |  |  |

| VS          | 1   | Input power supply pin to the controller. Connect a 100-nF capacitor across VS and GND pins.                                                                                                                                                                                                                                                |  |  |

| GATE        | 2   | Gate drive output. Connect to gate of the external N-channel MOSFET                                                                                                                                                                                                                                                                         |  |  |

| SRC         | 3   | Source pin. Connect to common source point of external back-to-back connected N-channel MOSFETs or the source pin of the high side switch MOSFET.                                                                                                                                                                                           |  |  |

| GND         | 4   | Ground pin                                                                                                                                                                                                                                                                                                                                  |  |  |

| EN          | 5   | EN/UVLO Input. Connect to VS pin for always ON operation. Can be driven externally from a micro controller I/O. Pulling the pin low below $V_{(ENF)}$ makes the device enter into low IQ shutdown mode. For UVLO, connect an external resistor ladder from input supply to EN/UVLO to ground.                                               |  |  |

| NC          | 6   | No connection                                                                                                                                                                                                                                                                                                                               |  |  |

| OV          | 7   | Adjustable overvoltage threshold input. Connect a resistor ladder from input supply to OV pin to ground. When the voltage at OV pin exceeds the overvoltage cutoff threshold then the GATE is pulled low. GATE turns ON when the OV pin voltage goes below the OVP falling threshold. Connect OV pin to ground when OV feature is not used. |  |  |

| VCAP        | 8   | Charge pump output. Connect to external charge pump capacitor.                                                                                                                                                                                                                                                                              |  |  |

| Thermal pad | •   | No connection.                                                                                                                                                                                                                                                                                                                              |  |  |

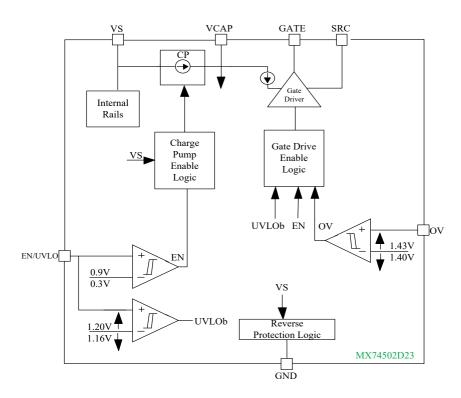

# **Block diagram**

# **Electrical characteristics**

$TJ = -40 ^{\circ} C \text{ to } +150 ^{\circ} C; \text{ typical values at } TJ = 25 ^{\circ} C, V(VS) = 12 \text{ V}, C(VCAP) = 1 \text{ } \mu\text{F}, V(EN/UVLO) = 3 \text{ V}, \text{ over operating free-air temperature range (unless otherwise noted)}$

| Symbol                                 | PARAMETER                                                   | TEST CONDITIONS                                                            | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| Vs SUPPLY VOLTA                        |                                                             |                                                                            |      |      |      |      |

| $V_{(VS)}$                             | Operating input voltage                                     |                                                                            | 4    |      | 85   | V    |

| V <sub>(VS_POR)</sub>                  | VS POR Rising threshold                                     |                                                                            | 3.10 | 3.40 | 4.10 | V    |

| V (VS_POR)                             | VS POR Falling threshold                                    |                                                                            | 3.05 | 3.35 | 3.75 | V    |

| V(VS POR(Hys))                         | VS POR Hysteresis                                           |                                                                            |      | 50   |      | mV   |

| $I_{(SHDN)}$                           | Shutdown Supply Current                                     | $V_{(EN/UVLO)} = 0V$                                                       | 0.3  | 0.7  | 1.2  | μΑ   |

| $I_{(Q)}$                              | Operating Quiescent Current                                 | I <sub>GND</sub> ,                                                         | 100  | 150  | 210  | μΑ   |

| I <sub>(REV)</sub>                     | VS pin leakage current during input                         | $0 \text{ V} \leq V_{(VS)} \leq -65 \text{ V}$                             |      | 25   |      | μA   |

|                                        | reverse polarity                                            | 0 V 2 V (VS) 2 -03 V                                                       |      | 23   |      | μΛ   |

| ENABLE INPUT                           |                                                             |                                                                            |      |      |      |      |

| V <sub>(EN_UVLOF)</sub>                | Enable/UVLO falling threshold                               |                                                                            | 1.08 | 1.16 | 1.25 | V    |

| $V_{(EN\_UVLOR)}$                      | Enable/UVLO rising threshold                                |                                                                            | 1.10 | 1.20 | 1.40 | V    |

| V <sub>(ENF)</sub>                     | Enable threshold voltage for low IQ                         |                                                                            | 0.30 | 0.70 | 0.90 | V    |

| V (ENF)                                | shutdown                                                    |                                                                            | 0.30 | 0.70 | 0.90 | V    |

| $V_{(EN\_Hys)}$                        | Enable Hysteresis                                           |                                                                            |      | 40   |      | mV   |

| I <sub>(EN/UVLO)</sub>                 | Enable sink current                                         | $V_{(EN/UVLO)} = 12V$                                                      |      | 1    |      | μΑ   |

| GATE DRIVE                             |                                                             |                                                                            |      |      |      |      |

|                                        | Peak source current                                         | $V_{(GATE)} - V_{(SRC)} = 5V$                                              | 5    | 12   | 20   | mA   |

| I <sub>(GATE)</sub>                    | D1i-1                                                       | EN= High to Low                                                            |      | 2.2  |      | Α    |

|                                        | Peak sink current                                           | $V_{(GATE)} - V_{(SRC)} = 5 \text{ V}$                                     |      | 2.3  |      | A    |

| D                                      | 4:1                                                         | EN = High to Low                                                           |      | 1.6  | 5    | 0    |

| R <sub>DSON</sub>                      | discharge switch R <sub>DSON</sub>                          | $V_{(GATE)} - V_{(SRC)} = 100 \text{ mV}$                                  |      | 1.6  | 3    | Ω    |

| CHARGE PUMP                            |                                                             |                                                                            |      |      |      |      |

|                                        | Charge Pump source current                                  | $V_{\text{(VCAP)}} - V_{\text{(VS)}} = 7V$                                 | 50   | 110  | 300  | 4    |

| τ                                      | (Charge pump on)                                            | $\mathbf{V}(VCAP) - \mathbf{V}(VS) - \mathbf{V}$                           | 30   | 110  | 300  | μΑ   |

| $I_{(VCAP)}$                           | Charge Pump sink current (Charge                            | V - 14V                                                                    |      | 4.0  | 5.5  | 4    |

|                                        | pump off)                                                   | $V_{(VCAP)} - V_{(VS)} = 14V$                                              |      | 4.0  | 3.3  | μΑ   |

| V V                                    | Charge pump voltage at $V_{(VS)}$ =                         | I                                                                          | 8    |      |      | V    |

| $V_{(VCAP)} - V_{(VS)}$                | 3.4V                                                        | $I_{(VCAP)} \le 30 \mu A$                                                  | 0    |      |      | V    |

| $V_{(VCAP)} - V_{(VS)}$                | Charge pump turn on voltage                                 |                                                                            | 10.3 | 11.6 | 13.0 | V    |

| $V_{(VCAP)} - V_{(VS)}$                | Charge pump turn off voltage                                |                                                                            | 11.2 | 12.9 | 14.2 | V    |

| V <sub>(VCAP)</sub> –V <sub>(VS)</sub> | Charge Pump Enable comparator                               |                                                                            |      | 1.3  |      | V    |

| $\mathbf{v}(VCAP) = \mathbf{v}(VS)$    | Hysteresis                                                  |                                                                            |      | 1.3  |      | V    |

| V <sub>(VCAP UVLO)</sub>               | V <sub>(VCAP)</sub> – V <sub>(S)</sub> UV release at rising |                                                                            | 5.3  | 6.2  | 7.1  | V    |

| V (VCAP UVLO)                          | edge                                                        |                                                                            | 3.3  | 0.2  | 7.1  | •    |

| V <sub>(VCAP UVLO)</sub>               | $V_{(VCAP)} - V_{(S)} UV$ threshold at                      |                                                                            | 4.7  | 5.1  | 5.6  | V    |

|                                        | falling edge                                                |                                                                            | 7.7  | 5.1  | 5.0  | v    |

| OVERVOLTAGE P                          |                                                             |                                                                            |      |      |      |      |

| $V_{(OVR)}$                            | Overvoltage threshold input, rising                         |                                                                            | 1.33 | 1.43 | 1.53 | V    |

| $V_{(OVF)}$                            | Overvoltage threshold input, falling                        |                                                                            | 1.30 | 1.40 | 1.50 | V    |

| V <sub>(OV Hys)</sub>                  | OV Hysteresis                                               |                                                                            |      | 30   |      | mV   |

| $I_{(OV)}$                             | OV Input leakage current                                    | $0V < V_{(OV)} < 5V$                                                       |      | 50   | 100  | nA   |

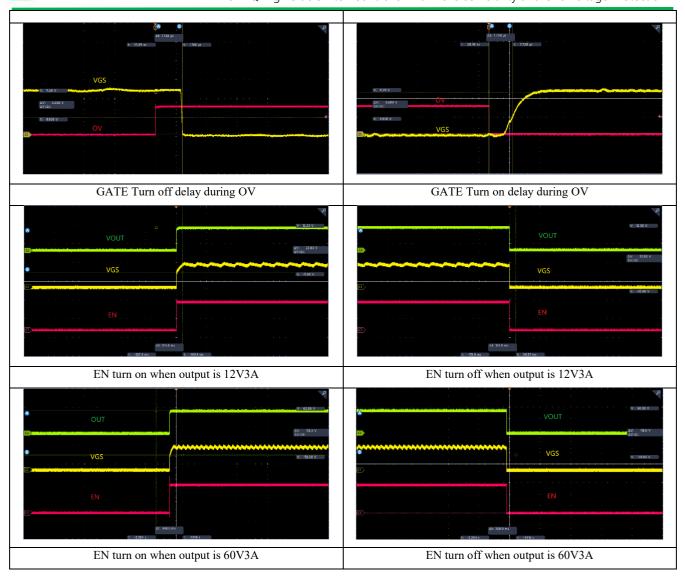

| SWITCHING CHAP                         | RACTERISTICS                                                |                                                                            |      |      |      |      |

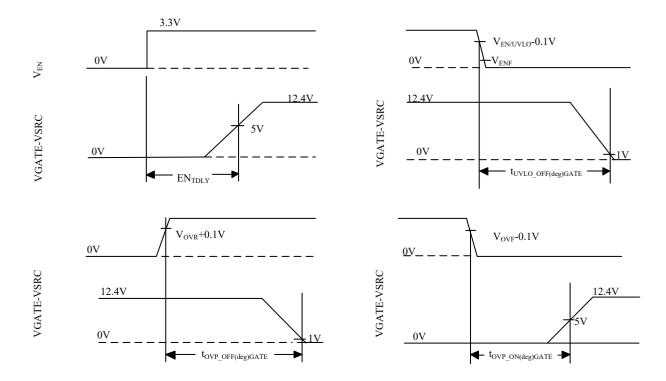

| ENTDLY                                 |                                                             | $V_{(VCAP)} > V_{(VCAP\ UVLOR)},$                                          | ]    |      |      |      |

|                                        | EN high to Gate Turn On delay                               | $V_{(EN/UVLO)} > V_{(EN\_UVLOR)}$ to $V_{(GATE-}$                          | 25   | 55   | 110  | μs   |

|                                        |                                                             | $_{SRC)} > 5V$ , $C_{(GATE-SRC)} = 1.5nF$                                  |      |      |      |      |

| fundo ocera y came                     | GATE Turnoff delay during                                   | $V_{(EN/UVLO)} \downarrow \text{to } V_{(GATE\text{-SRC})} <$              | 1    | 2    | 3.5  | 116  |

| tuvlo_off(deg)_gate                    | EN/UVLO                                                     | $1V,C_{(GATE-SRC)} = 1.5nF$                                                | 1    |      | 3.3  | μs   |

| town open a same                       | GATE Turnoff delay during OV                                | $V_{(OV)} \uparrow to V_{(GATE-SRC)} < 1V, C_{(GATE-SRC)}$                 | 1    | 2    | 3    | ше   |

| tovp_off(deg)_gate                     | GATE Turnoil delay during OV                                | SRC) = 1.5nF                                                               | 1    |      | 3    | μs   |

| torm over a second                     | GATE Turn on delay during OV                                | $V_{(OV)} \downarrow \text{ to } V_{(GATE-SRC)} > 5V, C_{(GATE-SRC)} > 5V$ | 4    | 7    | 10   | He   |

| tovp_on(deg)_gate                      | GATE Turn on delay during OV                                | SRC = 1.5nF                                                                | 4    | /    | 10   | μs   |

|                                        |                                                             |                                                                            |      |      |      |      |

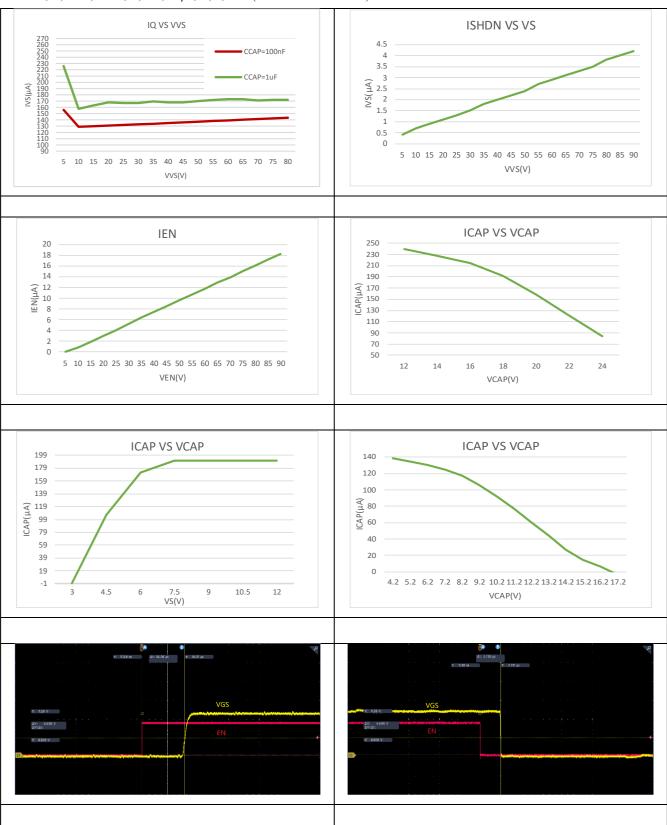

# **Characteristic plots**

$T_{\rm J}=25^{\circ}C,\ V_{\rm (ANODE)}=12V,\ C_{\rm (VCAP)}=1\mu F,\ V_{\rm (EN)}=3V\ (unless\ otherwise\ noted).$

# **Parameter Measurement Information**

# **Detailed description**

#### **Overview**

The MX74502D23 controller has all the features necessary to implement an efficient and fast reverse polarity protection circuit with load disconnect feature. This easy to uses reverse polarity protection controller is paired with an external back-to-back connected N-channel MOSFETs to replace other reverse polarity schemes such as a P-channel MOSFETs. The wide input supply range of 4V to 85V allows protection and control of  $12V_{\odot}$  24V  $_{\odot}$ 48V and 60V input supply systems. The device can withstand and protect the loads from negative supply voltages down to -90V. An integrated charge pump drives external back-to-back connected N-channel MOSFETs with gate drive voltage of approximately 13V. MX74502D23 with its fast gate drive strength of 8mA peak is suitable for applications which need fast turn-on and turn-off of external MOSFET switch. MX74502D23 features adjustable overvoltage protection using the OV pin. With the enable pin low during the standby mode, both the external MOSFETs and controller off and draws a very low shutdown current of 1µA.

#### **Input Voltage**

The VS pin is used to power the MX74502D23's internal circuitry, typically drawing  $150\mu A$  when enabled and  $1\mu A$  when disabled. If the VS pin voltage is greater than the POR Rising threshold, then MX74502D23 operates in either shutdown mode or conduction mode in accordance with the EN/UVLO pin voltage. The voltage from VS to GND is designed to vary from 85V to -90V, allowing the MX74502D23 to withstand negative voltage transients.

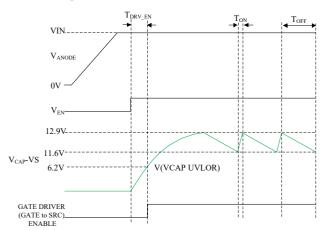

## **Charge Pump (VCAP)**

The charge pump supplies the voltage necessary to drive the external N-channel MOSFET. An external charge pump capacitor is placed between VCAP and VS pin to provide energy to turn on the external MOSFET. For the charge pump to supply current to the external capacitor the EN/UVLO pin voltage must be above the specified input high threshold,  $V_{(EN\_UVLOR)}$ . When enabled the charge pump sources a charging current of  $110\mu A$  typically. If EN/UVLO pins is pulled low, then the charge pump remains disabled. To ensure that the external MOSFET can be driven above its specified threshold voltage, the VCAP to VS voltage must be above the undervoltage lockout threshold, typically 6.2V, before the internal gate driver is enabled. Use the

following equation to calculate the initial gate driver enable delay

$$T_{(DRV\_EN)} = 75\mu s + C_{(VCAP)} \times \frac{V_{(VCAP\_UVLOR)}}{110\mu A}$$

where

- $\bullet$   $C_{(VCAP)}$  is the charge pump capacitance connected across VS and VCAP pin

- $V_{(VCAP\ UVLOR)} = 6.2V(typical)$

To remove any chatter on the gate drive approximately  $1000 \, \mathrm{mV}$  of hysteresis is added to the VCAP undervoltage lockout. The charge pump remains enabled until the VCAP to VS voltage reaches  $12.9 \, \mathrm{V}$ , typically, at which point the charge pump is disabled decreasing the current draw on the VS pin. The charge pump remains disabled until the VCAP to VS voltage is below to  $11.6 \, \mathrm{V}$  typically at which point the charge pump is enabled. The voltage between VCAP and VS continues to charge and discharge between  $11.6 \, \mathrm{V}$  and  $12.9 \, \mathrm{V}$  as shown in following figure. By enabling and disabling the charge pump, the operating quiescent current of the MX74502D23 is reduced. When the charge pump is disable, it sinks  $1 \, \mu A$  typical when  $12 \, \mathrm{V}$  input.

#### Gate Driver (GATE, SRC)

The gate driver is used to control the external N-Channel MOSFET by setting the appropriate GATE to SRC voltage.

Before the gate driver is enabled, the following three conditions must be achieved:

- The EN/UVLO pin voltage must be greater than the specified input high voltage.

- The VCAP to VS voltage must be greater than the undervoltage lockout voltage.

- The VS voltage must be greater than VS POR rising threshold.

If the above conditions are not achieved, then the GATE pin is

internally connected to the SRC pin, assuring that the external MOSFET is disabled. After these conditions are achieved, the gate driver operates in the conduction mode enhancing the external MOSFET completely.

#### Enable (EN/UVLO)

The MX74502D23 has an enable pin, EN/UVLO. The enable pin allows for the gate driver to be either enabled or disabled by an external signal. If the EN/UVLO pin voltage is greater than the rising threshold, the gate driver and charge pump operate as described in the Gate Driver (GATE, SRC) and Charge Pump (VCAP) sections. If the enable pin voltage is less than the input low threshold, the charge pump and gate driver are disabled placing the MX74502D23 in shutdown mode. The EN/UVLO pin can withstand a voltage as large as 85V and as low as -85V. This feature allows for the EN/UVLO pin to be connected directly to the VS pin if enable functionality is not needed. In conditions where EN/UVLO is left floating, the internal sink current of 2uA pulls EN/UVLO pin low and disables the device. An external resistor divider connected from input to EN/UVLO to ground can be used to implement the input Undervoltage Lockout (UVLO) functionality in the system. When EN/UVLO pin voltage is lower than UVLO comparator falling threshold (V<sub>EN/UVLOF</sub>) but higher than enable falling threshold (V<sub>ENF</sub>), the device disables gate drive voltage, however, charge pump is kept on. This action ensures quick recovery of gate drive when UVLO condition is removed. If UVLO functionality is not required, connect EN/UVLO pin to VS.

## **Overvoltage Protection (OV)**

MX74502D23 provides programmable overvoltage protection feature with OV pin. A resistor divider can be connected from input source to OV pin to ground in order to set overvoltage threshold. An internal comparator compares the input voltage against fixed reference (1.43V) and disables the gate drive as soon as OV pin voltage goes above the OV comparator reference. When the resistor divider is referred from input supply side, device is configured for overvoltage cutoff functionality. When the resistor divider is referred from output side (Vout), the device is configured for overvoltage clamp functionality.

When OV pin voltage goes above OV comparator V<sub>OVR</sub> threshold (1.43V typical), the device disables gate drive, however, charge pump remains active. When OV pin voltage falls below V<sub>OVF</sub> threshold (1.39V typical), the gate is quickly

turned on as charge pump is kept on and the device does not go through the device start-up process. When OV pin is not used, it can be connected to ground.

# **Device Functional Modes**

#### **Shutdown Mode**

The MX74502D23 enters shutdown mode when the EN/UVLO pin voltage is below the specified input low threshold  $V_{(ENF)}$ . Both the gate driver and the charge pump are disabled in shutdown mode. During shutdown mode the MX74502D23 enters low IQ operation with the VS pin only sinking  $1\mu A$  of current.

#### **Conduction Mode**

For the MX74502D23 to operate in conduction mode the gate driver must be enabled as described in the Gate Driver (GATE, SRC) section. If these conditions are achieved the GATE pin is Internally connected to the VCAP for fast turn-on of external FET in case of MX74502D23 gate drive is disabled when OV pin voltage is above  $V_{\rm OVR}$  threshold or EN/UVLO pin voltage is lower than  $V_{\rm EN/UVLOF}$  threshold.

# **Application and Implementation**

#### **Application Information**

The MX74502D23 is used with back-to-back connected N-Channel MOSFETs in a typical reverse polarity protection with load disconnect application. The schematic for the 48V input supply reverse polarity protection is shown in Typical Application diagram, where the MX74502D23 is used to drive the back-to-back connected MOSFETs Q1 and Q2 in series with a 48V supply.

#### **Typical Application**

## **Design Requirements**

A design example, system design parameters are shown in the following table.

| DESIGN PARAMETER       | EXAMPLE VALUE        |  |  |

|------------------------|----------------------|--|--|

| Input voltage range    | 48V nominal          |  |  |

| Overvoltage protection | 58V                  |  |  |

| Output current         | 8A full load         |  |  |

| Output capacitance     | 220μF typical output |  |  |

| Surput suparitunes     | capacitance          |  |  |

#### **Design Considerations**

- Input operating voltage range (including overvoltage protection)

- · Maximum load current

#### **MOSFET Selection**

The important MOSFET electrical parameters are the maximum continuous drain current  $I_D,$  the maximum drain-to-source voltage  $V_{DS(MAX)},$  the maximum gate-to-source voltage  $V_{GS(MAX)}$  and the drain-to-source on resistance  $R_{DSON}.$

The maximum continuous drain current,  $I_D$ , rating must exceed the maximum continuous load current. The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest differential voltage seen in the application. This requirement would include any anticipated fault conditions. The maximum  $V_{GS}$  MX74502D23 can drive is 13.8V, so a MOSFET with 15V minimum  $V_{GS}$  rating must be selected. If a MOSFET with  $V_{GS}$  rating < 15V is selected, a Zener diode can be used between GATE to SRC pin to clamp  $V_{GS}$  to safe level.

To reduce the MOSFET conduction losses, lowest possible  $R_{DS(ON)}$  is preferred. Selecting a MOSFET with  $R_{DS(ON)}$  that gives VDS drop 20mV to 50mV provides good trade off in terms of power dissipation and cost. As the load current is 8A, the MOSFET MX10T03AHT is ok for this application which the RDS(ON) is  $4m\Omega$  maximum.

Thermal resistance of the MOSFET must be considered against the expected maximum power dissipation in the MOSFET to ensure that the junction temperature (T<sub>J</sub>) is well controlled.

#### **Overvoltage Protection**

Resistors R1 and R2 connected in series is used to program the overvoltage threshold. Connecting R1 to VIN provides overvoltage cutoff and switching the connection to VOUT provides overvoltage clamp response. By calculating the following formula, the resistance value required to set the overvoltage threshold  $V_{\rm OV}$  to 58V is obtained.

$$V_{OVR} = \frac{R_2 \times V_{OV}}{R_1 + R_2}$$

For minimizing the input current drawn from the supply through resistors R1 and R2, it is recommended to use higher value of resistance. Using high value resistors adds error in the calculations because the current through the resistors at higher value becomes comparable to the leakage current into the OV pin. Select (R1 + R2) such that current through resistors is around 100 times higher than the leakage through OV pin. Based on the device's electrical characteristics,  $V_{\rm OVR}$  is 1.43V, select (R1) = 395k $\Omega$  and R2 = 10k $\Omega$  as a standard resistor value to set overvoltage cutoff of 58V.

#### Charge Pump VCAP, Input and output Capacitance

Minimum required capacitance for charge pump VCAP and input and output capacitance are:

- C<sub>VCAP</sub>: minimum recommended value of VCAP ( $\mu$ F)  $\geq$ 50 × Effective C<sub>ISS(MOSFET)</sub>( $\mu$ F), 0.22 $\mu$ F is selected

- C<sub>IN</sub>: typical input capacitor of  $0.1 \mu F$

- C<sub>OUT</sub>: typical output capacitor 220µF

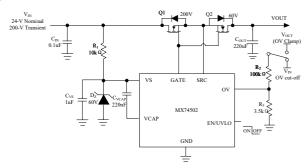

#### **Input Surge Stopper Using MX74502D23**

Many industrial applications need to comply with input overvoltage transients and surge events specified by standards such as IEC61000-4-x. MX74502D23 can be configured as input surge stopper to provide overvoltage along with input reverse supply protection.

As shown in the figure above MOSFET Q1 is used to turn off or clamp output voltage to acceptable safe level and protect the MOSFET Q2 and MX74502D23 from input transient. Note that only the VS pin is exposed to input transient through a resistor, R1. A 60V rated Zener diode is used to clamp and protect the VS pin within recommended operating condition. Rest of the circuit is not exposed to higher voltage as the MOSFET Q1 can either be turned off completely or output voltage clamped to safe level.

#### VS Capacitance, Resistor R<sub>1</sub> and Zener Clamp (D<sub>Z</sub>)

A minimum of  $0.1\mu F$   $C_{VS}$  capacitance is required. During input overvoltage transient, resistor R1 and Zener diode  $D_Z$  are used to protect VS pin from exceeding the maximum ratings by clamping

$V_{VS}$  to 60V. Choosing R1 =  $10k\Omega$ , the peak power dissipated in Zener diode  $D_Z$  can be calculated as follows.

$$P_{DZ} = V_{DZ} \times \frac{(V_{IN(MAX)} - V_{DZ})}{R_1}$$

Where  $V_{DZ}$  is the breakdown voltage of Zener diode. Select the Zener diode which can handle peak power requirement.

Peak power dissipated in resistor R1 can be calculated as follows

$$P_{R1} = \frac{(V_{IN(MAX)} - V_{DZ})^2}{R_1}$$

Select a resistor package which can handle peak power and maximum DC voltage.

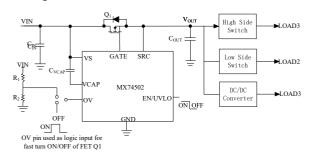

# Fast Turn-On and Turn-Off High Side Switch Driver Using MX74502D23

In applications such as industrial motor drives and safety power line communication digital output modules, N-Channel MOSFET based high side switch is very commonly used to disconnect the loads from supply line in case of faults such as overvoltage event. MX74502D23 can be used to drive external MOSFET to realize simple high side switch with overvoltage protection. The following diagram shows a typical application circuit where MX74502D23 is used to drive external MOSFET Q1 as a main power path connect and disconnect switch. A resistor divider from input to OV pin to ground can be used to set the overvoltage threshold.

If VOUT node (SRC pin) of the device is expected to drop in case of events such as overcurrent or short-circuit on load side, then additional Zener diode is required across gate and source pin of external MOSFET to protect it from exceeding its maximum V<sub>GS</sub> rating.

Many industrial safety applications require fast switching off of MOSFET to verify proper functioning of the high side disconnect switch for diagnostic purposes. MX74502D23H OV pin can be used as control input to realize fast turn-on and turn-off load switch functionality. With OV pin pulled above  $V_{\rm OVR}$  threshold of (1.43V typical), MX74502D23H turns off the external MOSFET (with Ciss = 4.7nF) within 1µs typically. When the OV

pin is pulled low, MX74502D23H with its peak gate drive strength of 8 mA turns on external MOSFET with turn on speed of  $8\mu s$  typical.

# **Power Supply Recommendations**

The MX74502D23 reverse polarity protection controller is designed for the supply voltage range of  $4V \le V_S \le 85V$ . If the input supply is located more than a few inches from the device, MAXIN recommends an input ceramic bypass capacitor higher than  $0.1 \mu F$ . To prevent MX74502D23 and surrounding components from being damaged under the conditions of a direct output short circuit, use a power supply having overload and short-circuit protection.

# Layout

## **Layout Guidelines**

- Place the input capacitor  $C_{IN}$  of  $0.1\mu F$  minimum close to VS pin to ground. This typically helps with better EMI performance.

- Connect GATE and SRC pin of MX74502D23 close to the MOSFET's GATE and SOURCE pin.

- Use thick traces for source and drain of the MOSFET to minimize resistive losses because the high current path of for this solution is through the MOSFET.

- The charge pump capacitor across VCAP and VS pin must be kept away from the MOSFET to lower the thermal effects on the capacitance value.

- The GATE pin of the MX74502D23 must be connected to the MOSFET gate with short trace. Avoid excessively thin and long running trace to the Gate Drive.

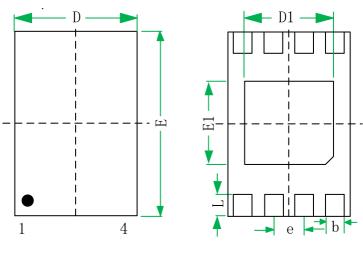

# **Package information**

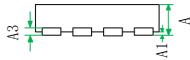

DFN2\*3-8L for MX74502D23

| SYMBOL | MILLIMETERS |          |      |  |

|--------|-------------|----------|------|--|

| SYMBOL | MIN         | NOM      | MAX  |  |

| A      | 0.5         | 0.55     | 0.6  |  |

| A1     | 0           | 0.025    | 0.05 |  |

| A3     |             | 0.152BSC |      |  |

| D      | 1.95        | 2        | 2.05 |  |

| E      | 2.95        | 3        | 3.05 |  |

| D1     | 1.5         | 1.65     | 1.75 |  |

| E1     | 1.65        | 1.8      | 1.9  |  |

| b      | 0.2         | 0.25     | 0.3  |  |

| e      |             | 0.500BSC |      |  |

| L      | 0.3         | 0.4      | 0.5  |  |

# **Restrictions on Product Use**

- ♦ MAXIN micro is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing MAXIN products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such MAXIN products could cause loss of human life, bodily injury or damage to property.

- ◆ In developing your designs, please ensure that MAXIN products are used within specified operating ranges as set forth in the most recent MAXIN products specifications.

- ◆ The information contained herein is subject to change without notice.

Version update record:

Preliminary: the original version.

V11: updated detailed electrical characteristics and block diagram.